# STUDY ON DIGITAL DOWN CONVERSION TECHNIQUE IMPLEMENTED ON FPGA

Athulya A PG Studies (DEC), Dept. of ECE Dayanandasagar College of Engineering, Bengaluru, Karnataka, India 560078

Abstract— The objective of this paper is to study the literature for FPGA based digital sown conversion technique for radars. The review of literature describes work done in the field of Radar technology. Elaborates the step by step improvements in the field of waveform generation and processing technology equipped in digital receivers. Radar technology primarily in the area of military applications is in an unceasing process of extending its capabilities. Phased array radars add to this process as it was initially invented for use in military radar systems to steer a beam of radio waves quickly across the sky to detect planes and missiles. High speed analog to digital converts employed in digital receivers digitize the received signal. The digitized signal is then down converted using digital signal processing techniques to obtain I and Q baseband signals. Basically, the signal is sampled by A/D converter, frequency shifted to baseband, low-pass filtered and decimated to produce I and Q digital data. The importance of how FPGA with a large RAM capacity provides an adequate storage for pulse width of most radar applications and high clock rates allows generation of high bandwidth waveform to enable greater radar resolution is described.

*Keywords*— Digital down conversion, Phased array radars, FPGA, Direct digital synthesizer.

# I. INTRODUCTION

The word "radar" is the abbreviation for "Radio Detection and Ranging" which is defined as the art of detecting target presence, determining its direction and distance and recognizing its character via radio waves. In modern radar design, phased array radar is very important and technology forming multiple electronic beams is the most important technology in a phased array radar. Phased array is an array of antennas within which the relative phases of the several signals feeding the antennas are varied in such a simplest way that the effective radiation pattern of the array is reinforced in a very desired direction and suppressed in undesired directions.<sup>[11]</sup> The echo that is received from radar is then processed by waveform processing unit which is implemented on FPGA based hardware. Modern day high density FPGAs are best suited for implementing these functionalities as they Dinesha P Professor, Dept. of ECE Dayanandasagar College of Engineering, Bengaluru, Karnataka, India 560078

provide high computational bandwidth. Also FPGA provides better performance with improved Spurious-Free Dynamic Range (SFDR); faster processing and inbuilt reconfigurability; reduction in power requirement, increased precision performance; excellent quadrature channel phase balance, increased temperature stability. The digital receiver consisting of analogue to digital converter is capable of digitizing the received signal. The digitized signal is down converted to I and Q baseband signal using digital processing techniques. The down converted signal is then passed through a low pass filter and decimated. This process helps gather knowledge about the interested data which is the overriding doppler

#### II. REVIEW OF LITERATURE

Shaya Karimkashi et al.[5] (2013) -"Cylindrical Polarimetric Phased Array Radar Demonstrator: Design and Analysis of a Frequency Scanning Antenna Array" presents the design, modelling and measurement results of a mid-size cylindrical polarimetric phased array radar. The author explains how beam scanning in the elevation is obtained using the frequency scanning concept while the azimuth scanning is achieved using both the commutation and the beam scanning. The antenna array operating at a frequency range of 2.7 GHz to 3 GHz consisting of 96 vertical column mounted on the surface of the cylinder was designed and modelled. A Taylor amplitude distribution was applied to a 19-element vertical linear array antenna and low sidelobe levels were obtained for both horizontal and vertical polarizations. It was shown that using multilayer microstrip technology resulted in very low cross polarization patterns. In addition, a very good isolation between the horizontal and vertical port was achieved.

Phased array technology has been evolving steadily with advances in solid-state microwave integrated circuits, analysis and design tools and reliable fabrication practices. The paper [6](2015) - "The Evolution of Modern Phased Array Architectures" explains that the next- generation phased arrays will employ high levels of digitization, enabling a wide range of capacity and performance improvements. The authors implement tile array architecture, which greatly reduces the number of printed circuit boards and connectors in the array, substantial cost reductions are also achieved. Explaining the tile architecture the authors gives a cost comparison between slat architecture and tile architecture. The comparison greatly

signify that tile architecture is better in terms of cost than slat architecture. The rapid evolution of digital processor technology foster the emergence of fully digital arrays, with significant improvements in performance. The use of solidstate microwave integrated circuits have enabled the widespread use of phased arrays in military systems, but the cost remains high. In this paper the authors proposed a design using high-volume commercial microwave manufacturing techniques which has the potential to dramatically lower the cost of phased arrays.

| Component           | Slat(\$/m <sup>2</sup> ) | Tile (\$/m <sup>2</sup> ) |  |

|---------------------|--------------------------|---------------------------|--|

| T/R chip set        | \$80,000                 | \$80,000                  |  |

| Die handling        | \$40,000                 | N/A                       |  |

| T/R module packages | \$400,000                | \$8000                    |  |

| RF boards           | \$150,000                | \$25,000                  |  |

| Cables & connectors | \$10,000                 | \$1,562                   |  |

| cooling             | \$180,000                | \$40,000                  |  |

| structure           | \$50,000                 | \$16,250                  |  |

| Assembly & test     | \$80,000                 | \$12,500                  |  |

| Total               | \$990,000/m <sup>2</sup> | \$183,312/m <sup>2</sup>  |  |

TABLE I: COST CONSIDERATION OF SLAT AND TILE ARCHITECTURE <sup>[6]</sup>

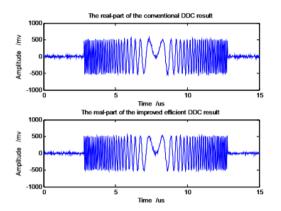

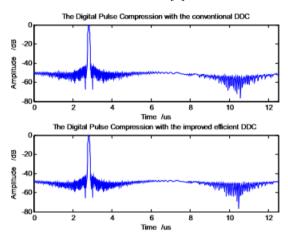

An improved design method for a digital down converter (DDC) is proposed in paper [7] (2012)- "A Highly Efficient Digital Down Converter in Wide Band Digital Radar Receiver". The proposed design by authors satisfy the increased requirements for miniaturization and low power consumption of signal processor in the digital wide band radar receiver. With this structure the resource utilization and digital signal complexity are both reduced significantly. compared to conventional development methods, FPGA based design results show that logical resources are saved by 83.6% and power consumption is reduced by 110mW, which shows the reliability and good engineering applicability of this process. Adopting the sampling technique that the system sampling frequency is 4 times as high as the intermediate frequency of the input signal and employment of half band FIR filters, the improved design method can save a large amount of logical resources, especially multiplier blocks.

Figure 1:Comparison of conventional and improved DDC results.[7]

Figure 2: Comparison of digital pulse compression results<sup>[7]</sup>

Yogesh P Sajjan et al.[8](2015) - "FPGA Based Digital Beam Forming for Phased Array Radar" describes a method to achieve digital beam forming in transmitter section. The authors describe the system by designing a sixteen channel direct - digital waveform synthesizer using direct digital synthesizer (DDS) to enable digital beam steering of the transmitting side for a 4x4 array patch antenna. Each antenna element has a separate beam forming exciter. DDS is a digitally controlled method of generating signals whose frequency, phase and amplitude are controlled by the respective description words. Also how the hardware is implemented in FPGA is mentioned. The DDS based digital beam forming developed has great potential to be used for multifunctional phased array radar, launch vehicles traffic controller, climate monitoring and in providing wind velocity data for aircraft.

The new generation of radar has to be equipped with a high performance exciters and receivers to cope with the threat in an Electronic warfare scenario. The threat in a complex environment with interfering signals requires a reliable signal generation with proper frequency agility and efficient gain controls in receiver system. Such a system is designed by LGM Prakasam et al.[9](2007) – "Digital Signal Generator

and Receiver design for S-band Radar". The design consists of exciter unit comprising of various digital modules for waveform generation, clocks and synchronization signal generation for different sub-systems of radar and digital code generation for the frequency to be synthesized. The utilization of the customized cores in the design models delivers high level of performance and area efficiency. Thus it resulted in an efficient implementation of the hardware using less percentage of FPGA resources. In addition, digital signals implementation proved to be advantageous because the system provided high flexibility, yet simple and reliable.

Digital multiple beam forming on every antenna element for a large phased array radar is not possible in processor based digital processing units, because it needs simultaneous processing of many A/D channels. As published in paper [10] (2014) - "A Digital multiple beam forming for phased array RADARs with parallel array processing", the authors have described methods to resolve this problem. The authors resolve the problem by using a multi array based beam forming technique with multiplexed signal processing unit on FPGA. The proposed mechanism employs multiplexed signal processing unit which is time shared for various beam formers. The technique ensures simultaneous beams without any compromise on functionality. In the proposed work the authors generated digital multiple beams with parallel array processing by using 16 antenna input signals. The design also provides a feasibility of implementing more than 16 antenna input signals.

TABLE II: BEAM FORMING SPECIFICATIONS.<sup>[10]</sup>

| Parameter                    | value            | comments                                              |

|------------------------------|------------------|-------------------------------------------------------|

| Input signal type            | Band pass signal | Coming from<br>typical<br>superheterodyne<br>receiver |

| Input signal frequency range | 1.5-3.5MHz       | 2 MHz BWand<br>2.5MHz IF<br>frequency value           |

| Sampling rate                | 10MHz            |                                                       |

| DDC filter size              | 16taps           |                                                       |

| DDC decimation               | 4                | DDC output<br>sampling rate<br>2.5Msps                |

| NCO values:COS               | 10.10            | As $f_0 = f_s / 4$                                    |

| NCO value:SIN                | 0.101            | As $f_0 = f_s / 4$                                    |

| Number of array elements     | 16               | Linear array                                          |

| Element spacing              | 3meters          |                                                       |

| DDS value | Angle  |

|-----------|--------|

| 8         | 11.25  |

| 20        | 28.125 |

| 80        | 112.5  |

| 128       | 180    |

TABLE III: TRUE ANGLE VALUES OF BEAM [10]

The proposed work by D.Subbarao et al.[11](2019) is more or less similar with the paper[5] mentioned above. The work "Multiple Digital Beamforming for Active Phased Array RADARs" implements methods to overcome the issue of processing A/D channels in digital multiple beam forming technology replacing antennas which hold large phased array radar by multiplexed signal processing unit. Working of each block in the system is explained briefly in the paper. The authors suggests the procedure of pillar shaping and the result of simulation and chip scope confirm maximum gain in desired direction.

A wideband linear frequency modulated continuous waveform (LFMCW) radar echo signal simulator design scheme which is based on Agilent N8241A arbitrary waveform generators and E8267D vector signal generator is described by Jianchao Wang et al.[12] (2016) – "Study on Wideband LFMCW Radar Echo Signal Simulate Technique". The radar signal wave data is produced by computer and is changed to wideband IQ baseband signal by N8241A. Then, the baseband signal is inputted to Agilent E8267D, which switch the baseband signal to microwave radio signal by its IQ modulate function and output, for testing wideband LFMCW radar in lab. Experiment result indicate that the simulator possess not only wide using performance and high precision but also have simplified structure.

Wu Changrui et al.[13] (2010) – "Design and FPGA implementation of flexible and efficient digital down converters" has designed and implemented digital down converter(DDC) on Xilinx FPGA virtex-5. Compared with traditional ASIC DDC devices, DDCs implemented by FPGA have more flexible frequency and phase characteristics and higher precision computation. Having analysed the key points of DDC theory and MATLAB simulation analysis the authors have designed a DDC a clock cross region and first in first out (FIFO) interface characteristics using Xilinx ISE. The paper majorly discusses the theory of DDC and the details of implementation on Xilinx FPGA. The paper also includes an application describing an example of data flow in one DDC.

Yingying Du et al[14] (2016) – "Digital down conversion design and implementation based on FPGA". The authors of the paper have brought out a unique method of implementing FPGA based digital down conversion. Digital free mixing scheme is proposed by the authors to achieve digital down conversion on the basis of digital mixing orthogonal

demodulation. This technique employed in the system will effectively reduce the computational complexity. The working principle is explained mainly including free mixing, design of cascade integrator comb filter and half band filter. FPGA implementation scheme is explained to prove the designed feasibility through software emulation.

Figure 3: Simulation diagram after low pass filter.<sup>[14]</sup>

Figure 4: Simulation diagram after CIC filter.<sup>[14]</sup>

Figure 5: Simulation diagram after half band filter.<sup>[14]</sup>

TABLE IV: SUMMARY OF REVIEW OF LITERATURE

| Authors                                                                                                                                               | Title                                                                                                                                       | Source        | year | Findings                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shaya<br>Karimkashi, Guifu<br>Zhang, Redmond<br>Kelley, John<br>Meier, Robert<br>Palmer, Allen<br>Zahrai, Richard J.<br>Doviak, and<br>Dusan S. Zrnic | Cylindrical<br>Polarimetric Phased<br>Array Radar<br>Demonstrator:<br>Design and<br>Analysis of a<br>Frequency<br>Scanning Antenna<br>Array | IEEE          | 2013 | Design, modelling and measurement results<br>of a mid-size cylindrical polarimetric phased<br>array radar.                                                                                                                                                                                                                                                                       |

| Jeffrey S. Herd,<br>David Conway M                                                                                                                    | The Evolution of<br>Modern Phased<br>Array Architectures                                                                                    | IEEE          | 2015 | Using a tile array architecture, which greatly<br>reduces the number of printed circuit boards<br>and connectors in the array, substantial cost<br>reductions are achieved                                                                                                                                                                                                       |

| Long Pang,<br>Bocheng Zhu, He<br>Chen, Yizhuang<br>Xie                                                                                                | A Highly Efficient<br>Digital Down<br>Converter in Wide<br>Band Digital Radar<br>Receiver                                                   | IEEE          | 2012 | Increased requirements for miniaturization<br>and low power consumption of signal<br>processor in the digital wide band radar<br>receiver.                                                                                                                                                                                                                                       |

| Yogesh P Sajjan,<br>Krishna R, Shahul<br>H                                                                                                            | FPGA Based<br>Digital Beam<br>Forming for Phased<br>Array Radar                                                                             | IJERGS        | 2015 | Method to achieve digital beam forming in<br>transmitter section. Implemented by<br>designing a sixteenchannel direct – digital<br>waveform synthesizer using Direct Digital<br>Synthesizer                                                                                                                                                                                      |

| LGM Prakasam,<br>Taniza Roy,<br>Meena.D                                                                                                               | Digital Signal<br>Generator and<br>Receiver design for<br>S-band Radar                                                                      | IEEE          | 2007 | High performance exciters and receivers to cope with the threat in an Electronic Warfare scenario.                                                                                                                                                                                                                                                                               |

| Nitesh Gaikwad,<br>Radha Krishna<br>AN                                                                                                                | A Digital multiple<br>beam forming for<br>phased array<br>RADARs with<br>parallel array<br>processing                                       | IOSR-<br>JVSP | 2014 | Inefficiency for simultaneously processing<br>many A/D channels is resolved by using<br>multi array based beam forming technique.                                                                                                                                                                                                                                                |

| D.Subbarao,<br>Tejavath Rama<br>Krishna                                                                                                               | Multiple Digital<br>beam forming for<br>Active Phased<br>Array RADARs                                                                       | IJRTE         | 2019 | Multi arraybased beam forming technique<br>with multiplexed signal processing unit on<br>FPGA is implemented for active phased<br>array radars                                                                                                                                                                                                                                   |

| JianchaoWang,<br>XiminLi,<br>JianhuiWu                                                                                                                | Study on Wideband<br>LFMCW Radar<br>Echo Signal<br>Simulate Technique                                                                       | IEEE          | 2016 | A wideband LFMCW radar echo signal<br>simulator design scheme which is based on<br>Agilent N8241A arbitrary waveform<br>generators and E8267D vector signal<br>generator is designed.                                                                                                                                                                                            |

| Wu Changrui,<br>Kong Chao, Xie<br>Shigen, Cai<br>Huizhi                                                                                               | Design and FPGA<br>implementation of<br>flexible and<br>efficient digital<br>down converters                                                | IEEE          | 2010 | The paper majorly discusses the theory of<br>DDC and the details of implementation on<br>Xilins FPGA. The paper also includes an<br>application describing an example of data<br>flow in one DDC. Designed a DDC a clock<br>cross region and first in first out (FIFO)<br>interface characteristics using Xilinx ISE by<br>analysing key points of DDC and Matlab<br>simulation. |

| Yingying Du,<br>Xinjing Ye, Yafei<br>Li, Zhengyu Cai                                                                                                  | Digital Down-<br>Conversion Design<br>and Implementation<br>Based on FPGA                                                                   | IEEE          | 2016 | The authors of the paper have brought out a<br>unique method of implementing FPGA based<br>digital down conversion. Digital free mixing<br>scheme is proposed by the authors to achieve<br>digital down conversion on the basis of<br>digital mixing orthogonal demodulation.                                                                                                    |

# III. CONCLUSION

The study of literature provides information of FPGA based digital down converters. The proposed systems in different papers shows the step by step improvements in the waveform processing unit at the digital receiver and also describes the pulse compression, advantages of using FPGA based architecture. A detailed study on the above mentioned topic is carried out in this paper. The summary of the literature is described in table IV. This study leads to a conclusion that digital down conversion technique offers good digital stability.

#### IV. ACKNOWLEDGEMENT

The present work is an effort to study digital down conversion technique implemented on FPGA for phased array radars. The paper titled – "Study on Digital Down Conversion Technique Implemented on FPGA" would not have been possible to come to the present shape without the work done by all the authors mentioned in references. With deep sense of gratitude we acknowledge all the authors mentioned in the references and their work.

#### V. REFERENCES

- [1] Radar handbook, third edition Merrill I. Skolnik Copyright © 2008 by The McGraw-Hill Companies.

- Fenn Alan J., Temme Donald H., Delaney William P., and Courtney William E. (2000). "The Development of Phased-Array Radar Technology", *Lincoln laboratory journal*, volume 12, number 2, (pp. 321-340)

- [3] <u>http://hunteng.co.uk/pdfs/tech/ddctheory.pdf</u> Theory of digital down conversion

- [4] <u>https://www.xilinx.com/products/silicon-</u> <u>devices/fpga/what-is-an-fpga.html</u> - Xilinx FPGA

- [5] Karimkashi Shaya, Zhang Guifu, Kelley Redmond, Meie John, Palmer Robert, Zahrai Allen, Doviak Richard J., and Zrnic Dusan S., (2013). "Cylindrical Polarimetric Phased Array Radar Demonstrator: Design and Analysis of a Frequency Scanning Antenna Array", *IEEE International Symposium on Phased Array Systems and Technology*, volume 2, (pp. 477-480)

- [6] Herd Jeffrey S., David Conway M (2015). "The Evolution of Modern Phased Array Architectures", *Proceedings of IEEE Journals and Magazines*, Volume 104, (pp.519-529)

- Pang Long, Zhu Bocheng, Chen He, Xie Yizhuang.

(2012). "A Highly Efficient Digital Down Converter in Wide Band Digital Radar Receiver", *IEEE 11<sup>th</sup> International Conference on signal processing*, Volume 3, (pp. 1795-1798)

- [8] Sajjan Yogesh P., R Krishna, H Shahul. (2015). "FPGA Based Digital Beam Forming for Phased Array Radar", *International Journal of Engineering Research and General Science*, Volume 3, (pp.531-536)

- [9] Prakasam LGM, Roy Taniza Roy, D Meena. (2007).

"Digital Signal Generator and Receiver design For Sband Radar", *IEEE Radar Conference*, (pp. 1049-1054)

- [10] Gaikwad Nitesh, A N Radha Krishna. (2014). " A Digital multiple beam forming for phased array RADARs with parallel array processing", *IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)* Volume 4, (pp.22-28)

- [11] D.Subbarao, Tejavath Rama Krishna. (2019).

"Multiple Digital beam forming for Active Phased Array RADARs", International Journal of Recent Technology and Engineering (IJRTE), Volume-7, (pp. 2035-2041)

- [12] Wang Jianchao, Li Ximin, Wu Jianhui. (2016). "Study on Wideband LFMCW Radar Echo Signal

Simulate Technique", *IEEE CIE International Conference on Radar*, (pp. 1634-1638)

- [13] Wu Changrui, Kong Chao, Xie Shigen, Cai Huizhi.

(2010). "Design and FPGA implementation of flexible and efficient digital down converters", *IEEE* 10<sup>th</sup> International Conference on Signal processing proceedings (ICSP2010), Vols I-III, (pp. 438-441)

- [14] Du Yingying, Ye Xinjing, Li Yafei, Cai Zhengyu, (2016). "Digital down converter design and implementation based on FPGA", 8th IEEE International Conference on Communication Software and Networks, (pp. 293-297).